PCIe LTSSM&Layer&Packet

目录

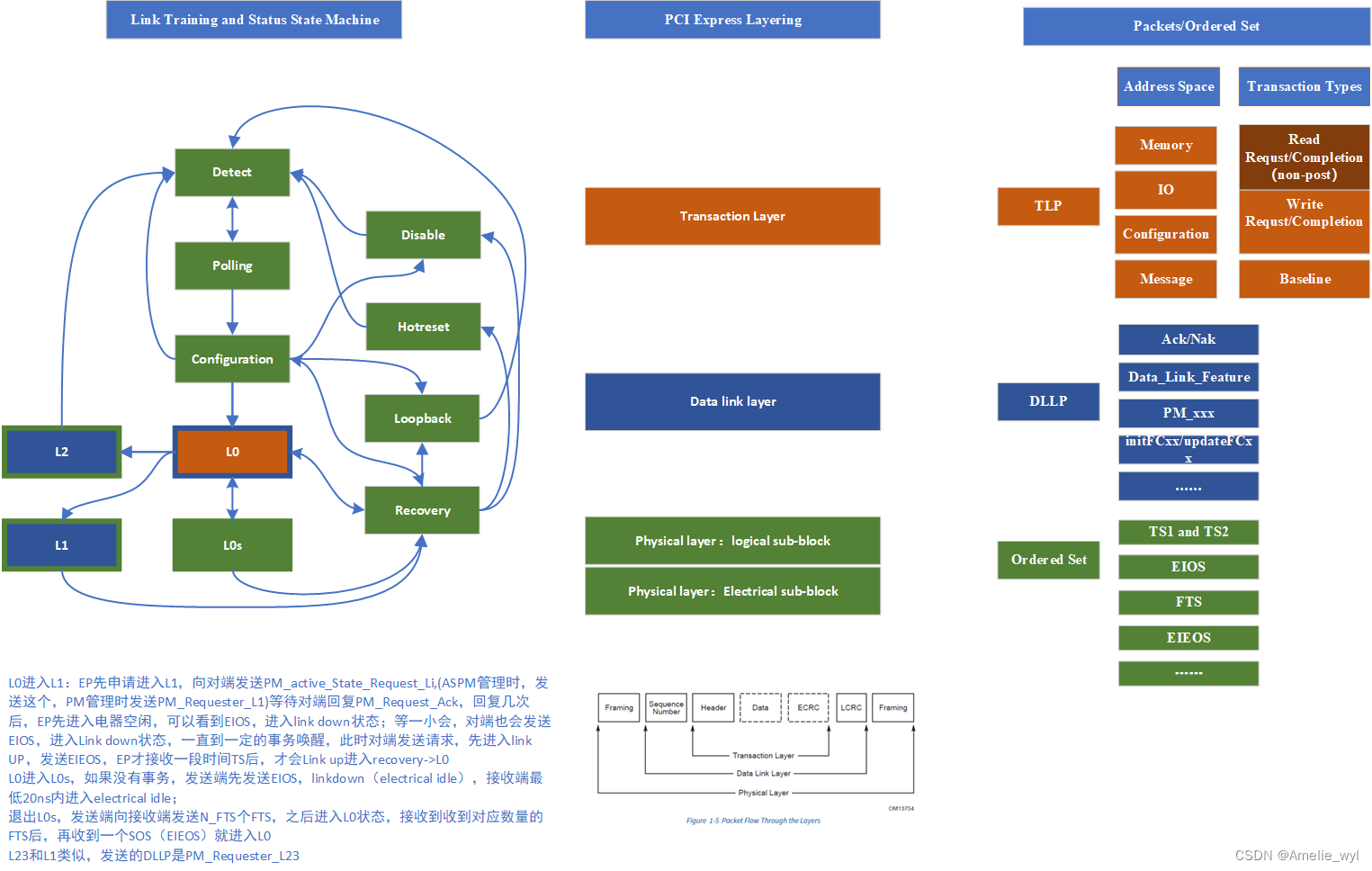

2、Layer

3、packet

transaction layer:TLP

data link layer:DLLP

physical layer:Ordered Set

颜色有一定的对应关系,不一定完全正确,仅限于个人理解,有误请指出~

1、LTSSM

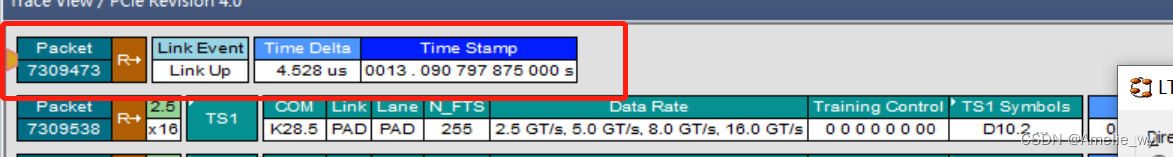

一个设备从上电正常从detect到L0的过程

1)首先是detect到对方,这个过程在分析仪上只有一个link up。如果想看到具体的可以使用示波器测detect信号,有时候不建链maybe与detect信号有关系,主要上升/下降时间和保持时间,如果一直停留在detect和polling中间可以试试将detect bypass

(3条消息) PCIE 设备在位检测机理_pcie detect_校哥-5207的博客-CSDN博客

(3条消息) PCIE switch与device不link问题_pcie detect波形_硬件技术交流的博客-CSDN博客

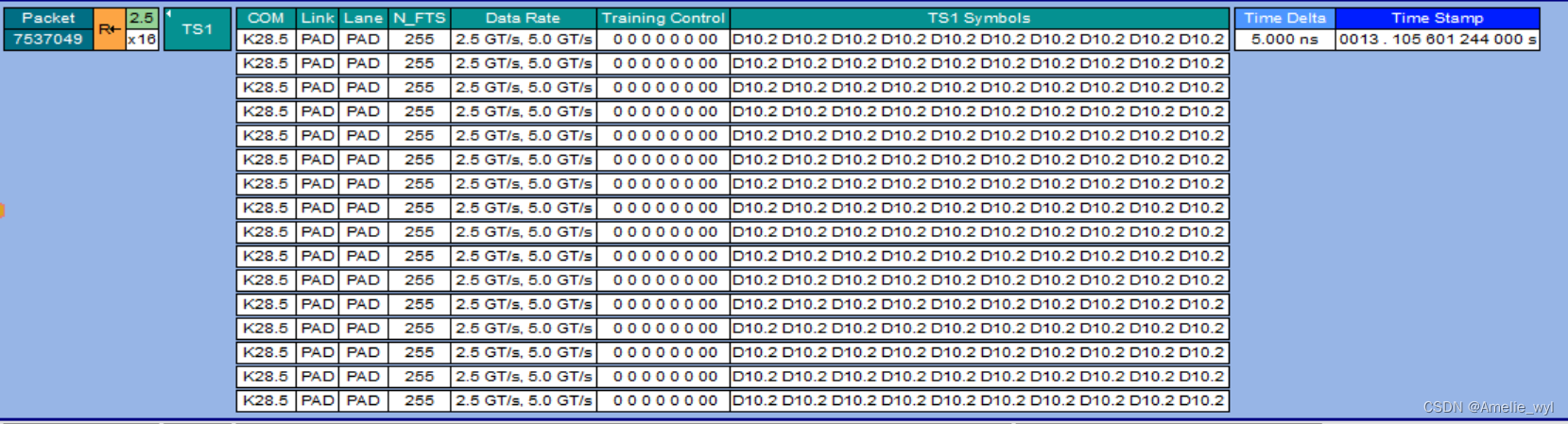

2)随后双方进入polling,这个阶段是bit锁定和symbol锁定,个人理解就是能“听懂”对方,正确识别到各个symbol为止。

In this state, bit lock and Symbol lock are established and Lane polarity is configured.(spec 4.2.5.2)

为避免测试进入polling.compliance,要配置允许电气探测宽度与协商宽度不一致。

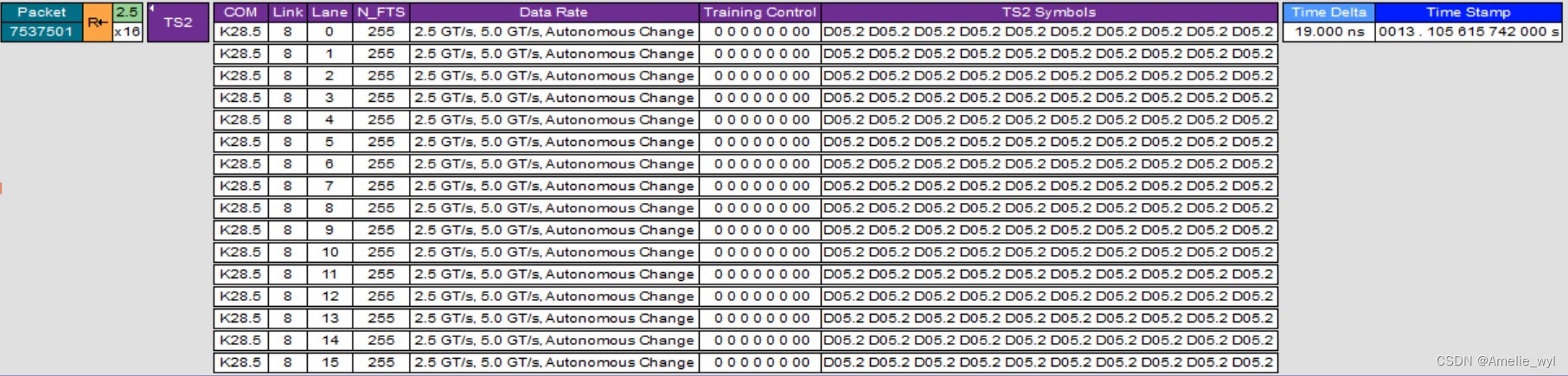

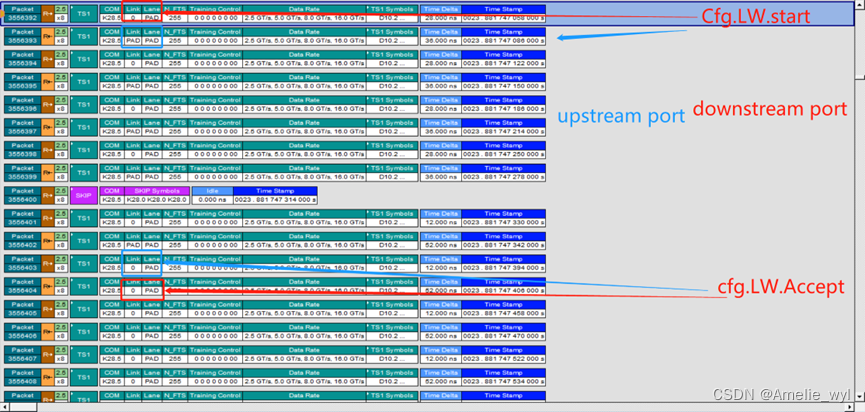

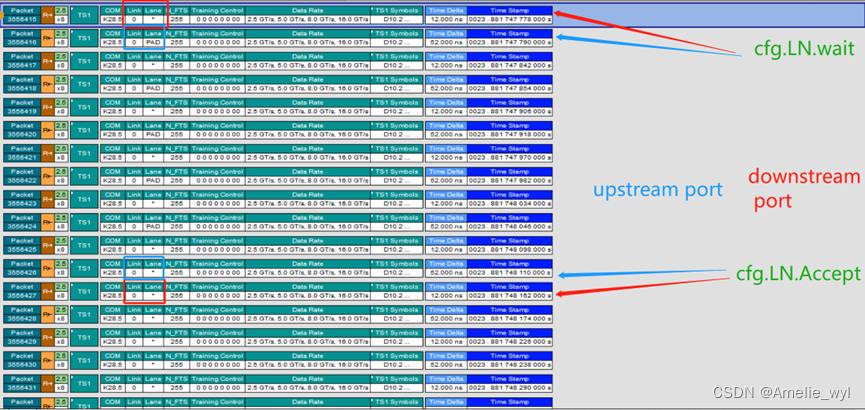

3)随后进入configuration,双方协商宽度,link number、lane number;两者在polling阶段都被填充为PAD symbol;最开始协商link number,后续协商lane number;

lane number:一般和物理lane数对应,x8设备一般就是lane0-lane7;

link number:如果lane需要分组需要使用,比如lane0-3接一个设备,lane4-7接一个设备,那么lane0-3可以协商为link 0,lane4-7 协商为link 1;当然,协商过程是先协商link number再协商lane number的;在目前我的实际应用中,link number一般都是一个固定的数,没有对lane进行分组,一般都是0(下图。。。是8,所以不分组的时候是几没啥作用);

In Configuration, both the Transmitter and Receiver are sending and receiving data at the negotiated data rate. ①The Lanes of a Port configure into a Link through a width and Lane negotiation sequence(link width,lane number). Also, ②Lane-to-Lane de-skew must occur(COM字符), scrambling can be disabled if permitted, ③the N_FTS is set, and the Disabled or Loopback states can be entered.(spec 4.2.5.3)

Downstream Lanes(Upstream Lanes(同 downstream port))

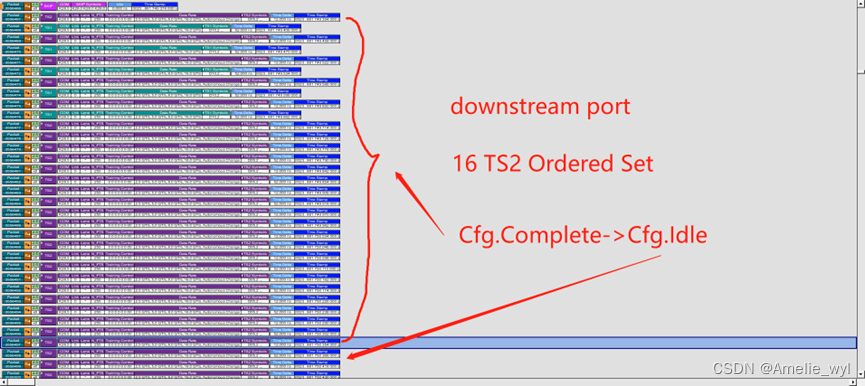

The next state is Configuration.Idle immediately after all Lanes that are transmitting TS2 Ordered Sets receive eight consecutive TS2 Ordered Sets with matching Lane and Link numbers (non-PAD) and identical data rate identifiers (including identical Link Upconfigure Capability (Symbol 4 bit 6)), and 16 TS2 Ordered Sets are sent after receiving one TS2 Ordered Set. (spec 4.2.6.3.5.1)

4)如果设备支持的最大速率是gen1,configuration之后就会进入L0;如果支持的最大速率是gen2/gen3/gen4,会进入recovery 进行切速,切速到gen3/4的recovery过程一般会进行EQ;recovery之后就进入L0,开始正常的DLLP,TLP发送接收了。

4.1) Recovery.RcvrLock

In Recovery, both the Transmitter a

Amelie_yalili

Amelie_yalili

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

8262

8262

暂无认证

暂无认证

Amelie_yalili: 配置空间里的

闻一鸣: Headerlog是tlp包里面的吗

千年老曹: 不错哦