超前进位加法器原理与设计

超前进位加法器原理与设计

一、行波进位加法器关键路径分析

N比特行波进位加法器可由N个全加器级联而成,电路的延迟包括门延迟和线延迟等,分析忽略线延迟。

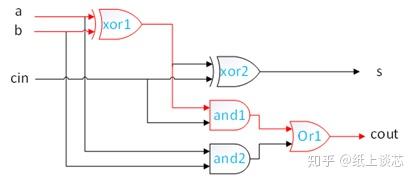

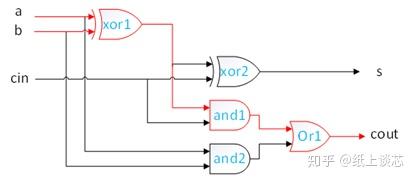

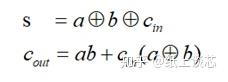

从输入a,b,cin到输出s和cout,有以下路径:

- a->s:经过xor1,xor2两个门电路

- b->s:经过xor1,xor2两个门电路

- cin->s:经过xor2一个门店路

- a->cout:经过xor1,and1,or1三个门电路

- b->cout:经过xor1,and1,or1三个门电路

- cin->cout:经过and2,or1两个门电路

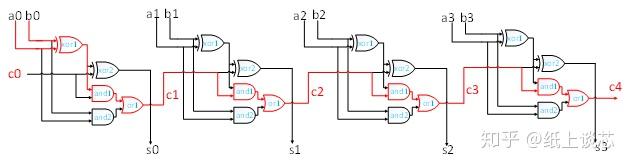

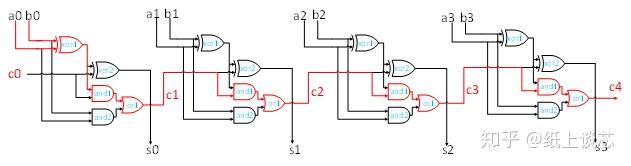

由这些路径可知,从a,b,cin输入数据准备好,到所有的s和cout完成,a或b到cout共有三个门电路延迟,是全加器的最长路径,且s不参与下一级全加器运算,cout将作为下一个cin输入继续计算下一级的s和cout。

由N个全加器级联的行波进位加法器除了第一个进位c1有3个门延迟外,剩余N-1个全加器生成进位需要2个门电路延迟,所以N比特行波进位加法器最长路径共有“(3+(N-1)*2)=2N+1”个门电路延迟,如上图4比特行波进位加法器,红色描绘的路径即是最长路径,共有2*4+1=9个门电路延迟。

二、超前进位加法器

对于更宽的加法器N,行波进位加法器关键路径越长,限制了加法器的性能,对于高速处理器等将是个极大的瓶颈。所以,本文介绍的超前进位加法器优化改进行波进位器的关键路径。RCA的缺点在于第k位的进位Ck必须依赖于前一级的Ck-1,所以最高位的进位将必须等待之前所有级进位计算完毕后才能计算出结果。所以,超前进位加法器的思想是并行计算进位Ck。

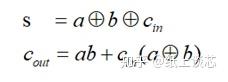

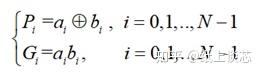

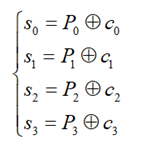

观察上式s和c,将共有部分分别定义:

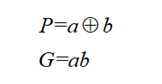

对于N比特LCA加法器,进位与和公式将重新书写如下:

其中:

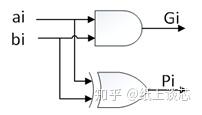

其门电路图如下,其实是个半加器:

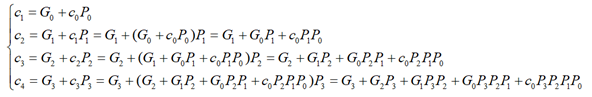

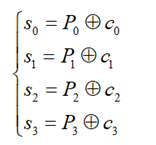

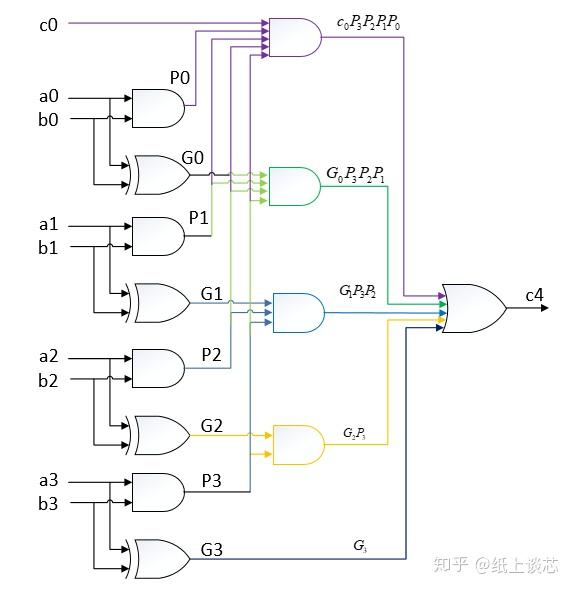

以4比特LCA加法器为例,其进位链与和公式分别计算如下:

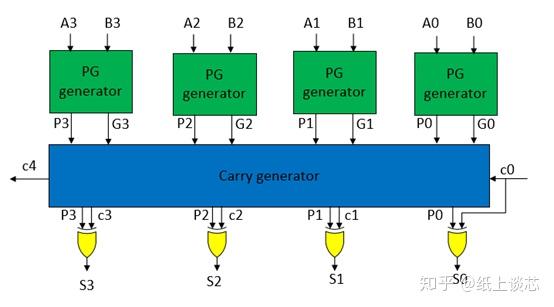

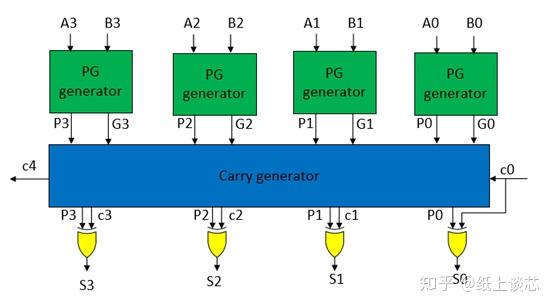

根据上述式子,可以计算出Ci和Si,其结构图为:

根据超前进位加法器中进位链c和输出s的物理实现方式不同,大致可分成以下三类:

- 递归超前进位加法器(Recursive Lookahead Carry Adder,简称RLCA)

- 分类超前进位加法器(Block Lookahead Carry Adder,BCLA),也称(section-carry-based carry-lookahead adder)

- 混合型超前进位加法器

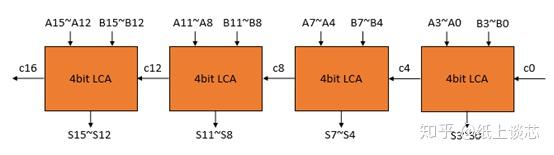

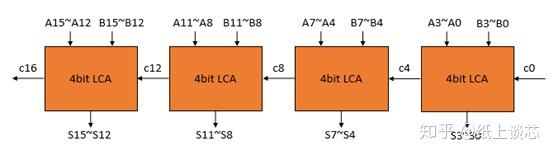

以上不同种类LCA之后细讲。对于位宽更大的LCA如16,32,64比特LCA等可以并行生成所有的PG和进位C,但这会造成电路极大的扇入和扇出;另外可以根据4比特LCA级联而成,如16比特LCA可由如下图级联而成(属RLCA):

三、超前进位加法器关键路径分析

为什么超前进位加法器在速度方面相比行波进位加法器更胜一筹?当然,从进位链的生成上也可以看出,我们从进位链C4来对比一下。

从输入所有的a,b和c0,LCA的输出进位c4只需要3级门电路延迟,c0,c1,c2,c3同时生成,同时由于S3=P3 xor c3,所以4比特LCA关键路径为4级门延迟。虽然经过了很多门电路,但他们的计算是同时的,而4比特RCA计算出c4需要9个门电路延迟。同样是32比特加法器,理想的LCA(全部展开所有的进位逻辑)关键路径延迟理论上只需要4个门电路,而RCA的关键路径延迟为65个门电路。如果采用4比特级联LCA,形成32比特LCA,则需要(3+7*2+1)=18级门电路延迟,相比RCA,缩短了关键路径的长度。

以上比较忽略多输入门延迟,真正的门电路延迟计算需根据不同的门电路库文件,且对AND/OR/NAND等门电路输入数目有限制,如通常的4输入。此处只可意会。

总而言之,RCA的缺点在于关键路径长,限制了速度,性能不高;LCA关键路径短,速度快,进位链计算依赖少,但对于位宽较大的加法器,PG和进位生成逻辑大,存在较大扇入扇出,变化信号多,会有较多的glitch,且面积与复杂度比同等的RCA大。

四、Verilog描述

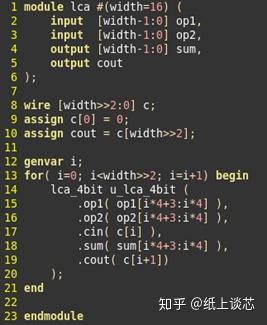

以下参数化LCA基于4比特LCA设计,width可参数化定义为4的倍数,如20,24,32等。

1万+

1万+

饺屿琪琪: 请问博主85行tm = tt.*5e-9;为什么乘这个量级

做而论道_CS: P = A B、 G = A (异或) B。 与、异或,它们两者,速度不一样。 “异或”所用的时间,是“与”的三倍。 把它们并列,就会因为它们的时间差。 使得 C4 的值,就会不稳定,出现 “毛刺”。 毛刺,这可是设计 “数字电路” 的大忌!

小猪乔治: 你说的这种是大小端

小猪乔治: 原文对的啊,你要说的是升降序吧?

胖芙: little_vect[0 +:8] 转化后一定是 little_vect[较小的数值 : 较大的数值] 这个地方不对吧,应该是[0 -:8]