Vivado-hls使用实例-详细教程

【引言】

本系列教程演示如何使用xilinx的HLS工具进行算法的硬件加速。

分为三个部分,分别为HLS端IP设计,vivado硬件环境搭建,SDK端软件控制。

在HLS端,要将进行硬件加速的软件算法转换为RTL级电路,生成便于嵌入式使用的axi控制端口,进行数据的传输和模块的控制。

点击查看工程源码

【HLS介绍】

HLS可以将算法直接映射为RTL电路,实现了高层次综合。vivado-HLS可以实现直接使用 C,C++ 以及 System C 语言对Xilinx的FPGA器件进行编程。用户无需手动创建 RTL,通过高层次综合生成HDL级的IP核,从而加速IP创建。

HLS的官方参考文档主要为:ug871( ug871-vivado-high-level-synthesis-tutorial.pdf )和ug902(ug902-vivado-high-level-synthesis.pdf)。

对于Vivado Hls来说,输入包括Tesbench,C/C++源代码和Directives,相应的输出为IP Catalog,DSP和SysGen,特别的,一个工程只能有一个顶层函数用于综和,这个顶层函数下面的子函数也是可以被综合的,会生成相应的VHDL和Verilog代码,所以,C综合后的RTL代码结构通常是跟原始C描述的结构是一致的,除非是子函数功能很简单,所需要的逻辑量很小。并不是所有的C/C++都可以被综合,动态内存分配和涉及到操作系统层面的操作不可以被综合。

Vivado HLS 的设计流程如下:

在整个流程中,用户先创建一个设计 C、C++ 或 SystemC 源代码,以及一个C的测试平台。通过 Vivado HLS Synthesis 运行设计,生成 RTL 设计,代码可以是 Verilog,也可以是 VHDL。有了 RTL 后,随即可以执行设计的 Verilog 或 VHDL 仿真,或使用工具的C封装器技术创建 SystemC 版本。然后可以进行System C架构级仿真,进一步根据之前创建的 C 测试平台,验证设计的架构行为和功能。设计固化后,就可以通过 Vivado 设计套件的物理实现流程来运行设计,将设计编程到器件上,在硬件中运行和/或使用 IP 封装器将设计转为可重用的 IP。

Step 1: 新建一个工程

1,Creat New Project新建文档,输入工程名称和工程路径。完成后点击Next。

2,添加设计文件,并制定顶层函数。完成后点击Next。

3,添加C语言仿真文件。完成后点击Next。

4,:配置Solution Name,一般默认即可。配置Clock Period,单位是ns。配置Uncertainty,默认为空。选择产品型号。完成后点击Finish。

5,工程新建成功后进入的开发界面,HLS是典型的Eclipse界面,和SDK的界面十分相似。

导入的文件的代码如下:

1,源文件。axi_interfaces.c

#include "axi_interfaces.h" void axi_interfaces (dout_t d_o[N], din_t d_i[N]) {<span class="token keyword">int</span> i<span class="token punctuation">,</span> rem<span class="token punctuation">;</span>

// Store accumulated data static

dacc_t acc[CHANNELS];

axi_interfaces_label0:

for (i=0;i<CHANNELS;i++)

{

acc[i] = 0;

}

// Accumulate each channel

For_Loop:

for (i=0;i<N;i++)

{

rem=i%CHANNELS;acc[rem] = acc[rem] + d_i[i];d_o[i] = acc[rem];

}

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

2,头文件。axi_interfaces.h

#ifndef AXI_INTERFACES_H_

#define AXI_INTERFACES_H_

#include <stdio.h>

typedef int din_t;

typedef int dout_t;

typedef int dacc_t;

#define CHANNELS 8

#define SAMPLES 4

#define N CHANNELS * SAMPLES

void axi_interfaces (dout_t d_o[N], din_t d_i[N]);

#endif

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

3,测试文件。axi_interfaces_test.c

#include "axi_interfaces.h"

int main () {

// Create input data

din_t d_i[N] = { 10, 20, 30, 40, 50, 60, 70, 80,

11, 21, 31, 41, 51, 61, 71, 81,

12, 22, 32, 42, 52, 62, 72, 82,

13, 23, 33, 43, 53, 63, 73, 83};

dout_t d_o[N];

int i, retval=0;

FILE *fp;

// Call the function to operate on the data

axi_interfaces(d_o,d_i);

// Save the results to a file

fp=fopen(“result.dat”,“w”);

fprintf(fp, “Din Dout\n”);

for (i=0;i<N;i++) {

<span class="token function">fprintf</span><span class="token punctuation">(</span>fp<span class="token punctuation">,</span> <span class="token string">"%d %d\n"</span><span class="token punctuation">,</span> d_i<span class="token punctuation">[</span>i<span class="token punctuation">]</span><span class="token punctuation">,</span> d_o<span class="token punctuation">[</span>i<span class="token punctuation">]</span><span class="token punctuation">)</span><span class="token punctuation">;</span>

}

fclose(fp);

// Compare the results file with the golden results

retval = system(“diff --brief -w result.dat result.golden.dat”);

if (retval != 0) {

printf(“Test failed !!!\n”);

retval=1;

} else {

printf(“Test passed !\n”);

}

// Return 0 if the test passes

return retval;

}

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

- 34

- 35

- 36

- 37

- 38

- 39

- 40

- 41

- 42

- 43

- 44

- 45

- 46

- 47

- 48

- 49

- 50

- 51

- 52

- 53

- 54

- 55

- 56

- 57

- 58

- 59

- 60

4,测试数据。result.golden.dat

Din Dout

10 10

20 20

30 30

40 40

50 50

60 60

70 70

80 80

11 21

21 41

31 61

41 81

51 101

61 121

71 141

81 161

12 33

22 63

32 93

42 123

52 153

62 183

72 213

82 243

13 46

23 86

33 126

43 166

53 206

63 246

73 286

83 326

- 1

- 2

- 3

- 4

- 5

- 6

- 7

- 8

- 9

- 10

- 11

- 12

- 13

- 14

- 15

- 16

- 17

- 18

- 19

- 20

- 21

- 22

- 23

- 24

- 25

- 26

- 27

- 28

- 29

- 30

- 31

- 32

- 33

Step 2: C源代码验证

本步骤是对功能代码的逻辑验证,相当于功能前仿。

1,测试程序的代码入下图。该程序先调用综合的函数,得到计算结果,再和预先的数据集进行比较,最后返回计较的结果。计算结果和预先的数据集一致时,测试通过,不一致时,测试失败。需要查看代码,寻找错误。

按钮,开始C源代码验证。

3,验证的结果显示在控制栏中。如图显示,测试通过。

4,在头文件中,重定义了数据类型,参数,并进行了函数声明。

Step 3: 高层次综合

本步骤是把功能代码的综合成RTL逻辑。

1,点击红框中的按钮,将C代码综合成RTL。综合完成后,查看结果。

2,综合完成后,查看综合报告。包括时序,延时,资源占用,端口信息等。

3,端口分析。

(1)控制端口用于控制和显示该模块的工作状态。各个端口的功功能如下,默认情况下会生成下面四个控制端口。

ap_start(in):为高时,该模块开始处理数据。

ap_done(out):为高时,表示模块处理数据完成。

ap_idle(out):表明模块是否处于空闲态。高电平有效。为高时,该处于空闲态。

ap_ready(out):为高时,表示模块可以接受新的数据。

(2)数据端口用于传递模块的输入输出参数。

参数d_o,d_i 为数组类型,故默认状态下回生成内存接口。内存接口 (数组类型参数)数据来自外部的memory,通过地址信号读取相应的数据,输入到该模块中。输入数组从外部内存中读源数据,输出数组从向外部内存写入结果数据。各个端口的定义如下。

address:地址信号

ce0:片选信号

we0:写使能信号

d0 :数据信号

4,综合结果分析。

在分析界面,可以看到模块的运行情况。包括数据依赖关系和各个周期执行的操作,IO口的读写,内存端口的访问等等。

Step 4: 综合优化

在使用高层次综合,创造高质量的RTL设计时,一个重要部分就是对C代码进行优化。

Vivado HLS拥有自动优化的功能,试图最小化loop(循环)和function(函数)的latency。除了自动优化,我们可以手动进行程序优化,即用在不同的solution中添加不同的directive(优化指令)的方法,进行优化和性能对比。其中,对同一个工程,可以建立多个不同的solution(解决方案),为不同的solution添加directive可以达到如下目的。

优化的类型可分为如下类别:

端口优化。指定不同类型的模块端口。

函数优化。加快函数的执行速度,减小执行周期。

循坏优化。利用展开和流水线形式,减小循环的执行周期。

1,点击下面红框的图标,新建solution。

2,不同solution位于不同的文件夹中。

3,选中综合文件。可以在direct框中看可进行优化的标签。

4,双击选择d_o,选择interface,s_axilite。点击ok。将d_o的端口类型设置为s_axilite类型。

5,参考d_o,将d_i的接口类型也设置为s_axilite。将d_i的端口类型设置为s_axilite类型。

6,双击选择函数名称axi_interface,选择interface,s_axilite。点击ok。将控制端口的端口类型设置为s_axilite类型。

7,双击循环标签,选择流水线优化(pipeline),点击ok。

8,双击循环标签,选择循环展开优化(unroll),点击ok。

9,同上,也将标签为for_loop的循环进行流水线和展开优化。

10,最终的优化情况总结如下。

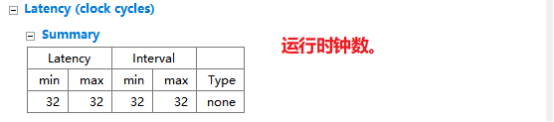

11,重新进行函数综合,查看综合报告如下。

12,分析。

同未优化相比,优化过后的函数综合后生成的模块的运行时钟大大减小。端口的接口类型也变为了axi_lite端口。但资源占用率有所增加,也体现了用资源换速度的设计理念。

Step 5: 综合结果文件

综合完成后,在各个solution的syn文件夹中可以看到综合器生成的RTL代码。包括systemc,VHDL,Verilog。

Step 6: 导出IP

在菜单里Solution>Export TL,设置如下,点击ok。

IP封装完成后,会在impl文件夹中输出ip文件夹,其中包含了RTL代码(hdl),模块驱动(drivers),文档(doc)等信息,其中包含一个压缩包文件,是用于建立vivado工程所用的IP压缩包。

Step 7: 总结

本文重点讲解了hls软件的使用方法和优化方法,在C语言模块设计上没有重点讲解。在掌握了hls软件的基本用法和优化方法后,接下来就可以设计更加复杂的C语言模块,进行rtl综合,加快设计开发的速度。

3080

3080

暂无认证

暂无认证

ちよぅなら: 博主您好,可以用米联客的开发板+adrv9002吗?

ちよぅなら: 您学会了吗,可以向您请将一些问题吗???

ybyt008: P2-P9是3.3V的数据,P1还是接1.8V吗?

月是故乡明513: 您好,请问一下10G Ethernet subsystem ip的mac_tx/rx_configureration_vector,还有pcs_pma[535:0]寄存器该怎么配置呢

FPGA_Linuxer: sun8002-a