CSI2与CDPHY学习

注意:本文是基于CSI2-V3.0 spec。

其中CPHY为 V2.0

DPHY为V2.5

本文主要在packet级别介绍CSI2与对应的CDPHY,需要注意的是:

CDPHY的HS burst数据和LPDT都是以packet为单位传输数据。

其中LPDT包括Escape和ALP的LPDT

1.CSI-CPHY

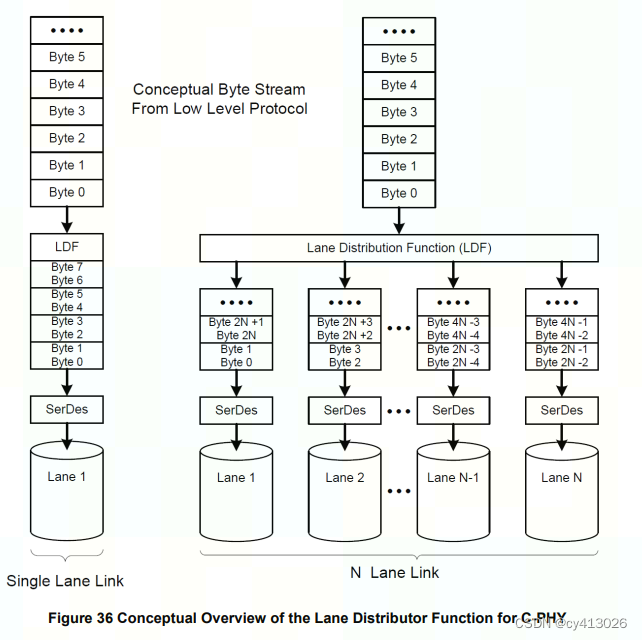

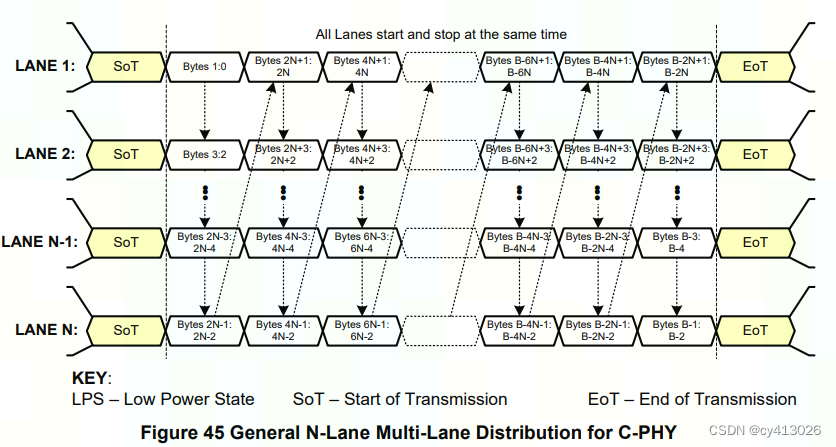

1.1CPHY的多lane分配与合并

- csi-cphy规定至少需要一条lane用于传输视频,最大lane数并没有做规定

- cphy是以16bit为传输单元

- csi protocol层将packet按16bit顺序平均分配到各条lane上

- packet长度为16bit对齐

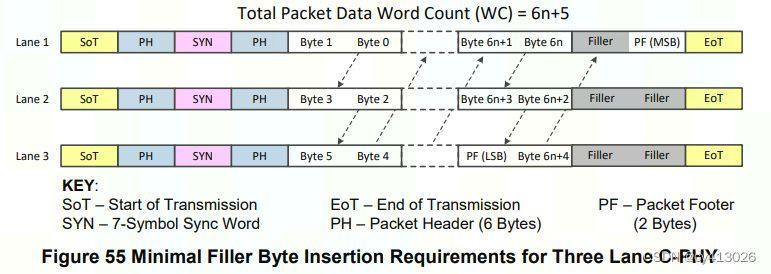

- 每条lane传输数据同时开始,同时结束。通过对packet footer FILLER字段填充保证所有lane数据量相等,也即packet长度是2N的整数倍个Byte(N为lane数)

下图给出多lane分配概念图

下图为多lane合并概念图

下图给出N Lane分配图,可以看出所有lane同时开始,同时结束。

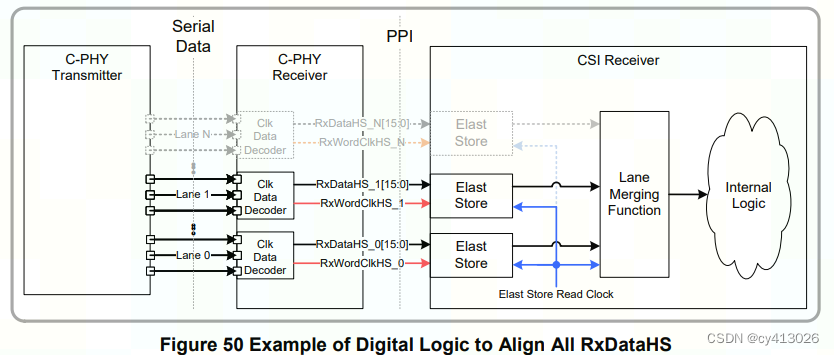

由于CPHY的每条lane 在RX端都会恢复出自己的wordClkHS,所以在多lane merge的时候为了保证各lane之间的同步,需要用ElastBuff做deskew。EBuff写入端clk是各lane恢复的wordClkHs,读clk是公用一个wordClkHs

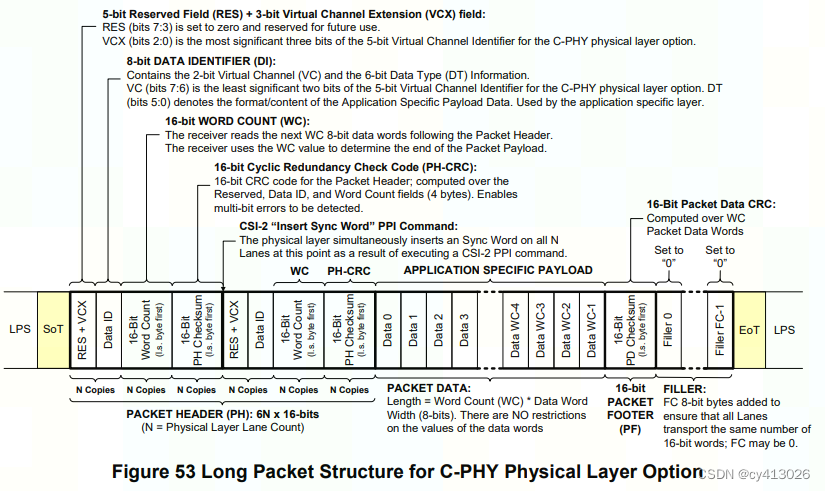

1.2 CPHY的长包格式

- 包头packet header共有2N份相同的3x16bit组成,每条lane2份。每条lane上的两份PH用syncWord隔开【总共添加了N份syncWord】。

- 把每条lane上的2份PH分别叫做main PH和redundant PH

- 从上图来看PH的16bit有连续N份,按照多lane分配原则,正好每条lane上一份,main PH分配完毕,ppi接口指示插入syncWord,然后开始分配redundant PH

- 可以看到该packet的PH没有ECC,不能进行PH的一bit纠错,所以才用了redundant PH和每条lane都发送PH的策略

- PH的checkSum只能检错

- payload可能不是16bit的整数倍,所以需要PF的FILLER字段填充到2Nx16的整数倍

- PF的checkSum是对payload的数据进行检错

- PF不需要备份,按顺序在各lane上分配就行

- 有5bit的VC ID,其中VCX 3bit+DataID[7:6],所以支持32个虚拟通道

- DataID[5:0] 标识数据类型DT(Data Type)

- 长包payload数据没有明显的限制,能够用16bitWC表示就行

- 图像长包CSI要求必须是一行为一包,无论CDPHY【但DSI没有这个限制】

VC是和sensor通道绑定的,一个VC里面可以传输不同的DT【一段时间采样YUV,一段时间采样RAW】.同一个VC里面不同DT的packet可以交织;不同VC的packet也可以交织

下图给出了payload为6n+5 byte时,各lane的数据分配情况。

1.2.1 CSI-CPHY长短包都不用ECC

CSI-CPHY不用ECC的原因是因为 CPHY对7-symbol进行线态编码的时候,利用的是线态变化表示数据,也即线态之间有联系,一但出现一个线态错误,会导致译码出现多个bit错误,这时ECC根本就无法纠错,所以采用了对重要信息PH和短包进行CRC checkSum的检错方法+冗余备份的形式进行纠错

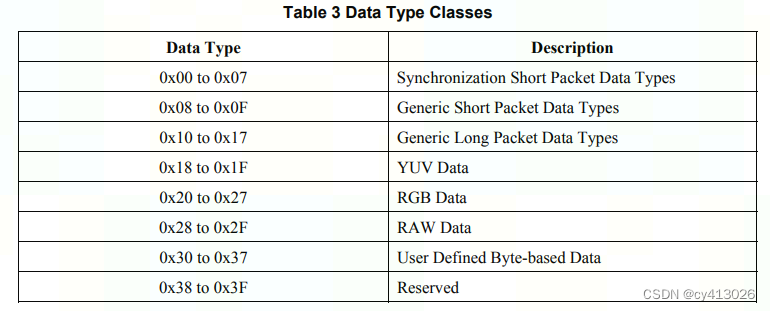

1.2.2 DataType(DT)

这里单独把DataType拿出来,是要强调一点数据包除了传输图像数据的长包和图像帧/行同步信息的短包之外还可以传输Generic Data【配置和状态寄存器等】及自定义Data。

LPDT按packet传输数据,且不会去传输图像数据。

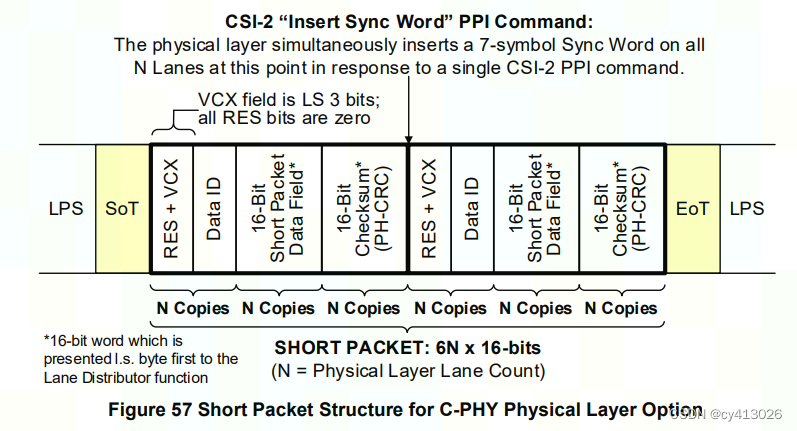

1.3CPHY的短包格式与SyncTiming

- 短包长度和长包PH一致

- 和长包的PH冗余是一样的,2N个3x16bit,每条lane上的前3x16bit和后3x16用syncWord隔开

- 短包没有payload,只有16bit short packet Data

- 有5bit的VC ID,其中VCX 3bit+DataID[7:6],所以支持32个虚拟通道

- DataID[5:0] 标识数据类型,包括Frame start(FS),frame end(FE)和line start(LS),line end(LE)类型短包

虽然长包payload 没有限制,但是对于图像长包(DT 0x18~0x2F)payload可以只能是一行video数据。

Note:无论C/DPHY的CSI图像长包都是一行一包,DSI的长包没有这个要求。

本人猜测CSI对V/Hsync的timing没有要求,所以接收一行数据不用缓存,接收完一行数据之后可以进入LP。而DSI在sink侧是要恢复V/Hsync的timing,需要存储,所以包长小于行长,存储可以减少,但一般DSI都支持一行的包长。

对于CSI/DSI的图像数据长包 都不应该有大于行长的LgP。因为中间是可以LP的。数据不会连续的。

短包包括两大类:

- 同步短包 FS/FE LS/LE EOTp

- 通用短包:包括传输一些快门打开/关闭,闪光灯触发等信息

正常burst传输情况下,FS/FE,LS/LE不需要像素级别的和payload对齐,如果需要像素级的V/HSync和水平垂直blanking区间timing,则可以按间隔要求发送short packet

1.3.1 FS/FE LS/LE与扫描方式和VC/DT的关系

FS/FE和LS/LE是和对应图像数据长包绑定的,能传输图像数据的长包DT为0x18---0x2F.长包还能传输非图像数据及自定义数据【这些DT不需要FS/FE/LS/LE】。

FS/FE和LS/LE的VC一定是和对应的图像数据长包VC一致的。

1.3.1.1 FS/FE

FS/FE和LS/LE都属于短包的数据类型,且都属于同步类短包:

从上表可以看到:

- EOT的短包EOTp,注意这个和EOT流程是不一样的,EOTp是在HS发送数据,EOT是向LP mode切换的结束流程,这里不在详细介绍

- LS/LE/EOTp都是可选的,FS/FE必须的

协议上给出FS/FE的16bit shortPacket date就是frame num。这个frame num不是实际的framenum 而是用来表示一个VC的完整帧和两帧的前后顺序。

- frameNum从1开始,0表示无效

- 每一个VC的帧独立计数【和DT无关】

- 每帧帧号增加1或2【以2为步长增加只有在发送端有些帧被masked,没有被发送】

- 每隔一段时间reset to 1

例如:

1,2,1,2,1,2,1,2

1,2,3,4,5,1,2,3,4,5

1,3,5,1,3,5

1,2,4,1,2,4

1.3.1.2 LS/LE

LS/LE并不是必须的,一旦某VC的某DT的某一帧包含了LS/LE,则该VC和DT的这一帧所有行都要有LS/LE。

LS和对应的LE的shortPacket data是16bit的lineNum,和frameNum一样这并不是一个实际的lineNum。当然等于实际的lineNum也没有问题。lineNum有下面三种使用方式

- 行号为0,不起作用

- 同一VC和DT的LS lineNum每次增加1,FS之后的第一个LS行号会定期重置为1,不一定是每个FS之后都置为1------这种情况预期是用于逐行扫描帧

- 同一VC和DT的LS lineNum每次增加x(x>1),FS之后的第一个LS行号会定期重置为非0起始值,连续帧之间的起始值可以不同,不一定是每个FS之后都重置-----这种情况预期是用于隔行扫描帧

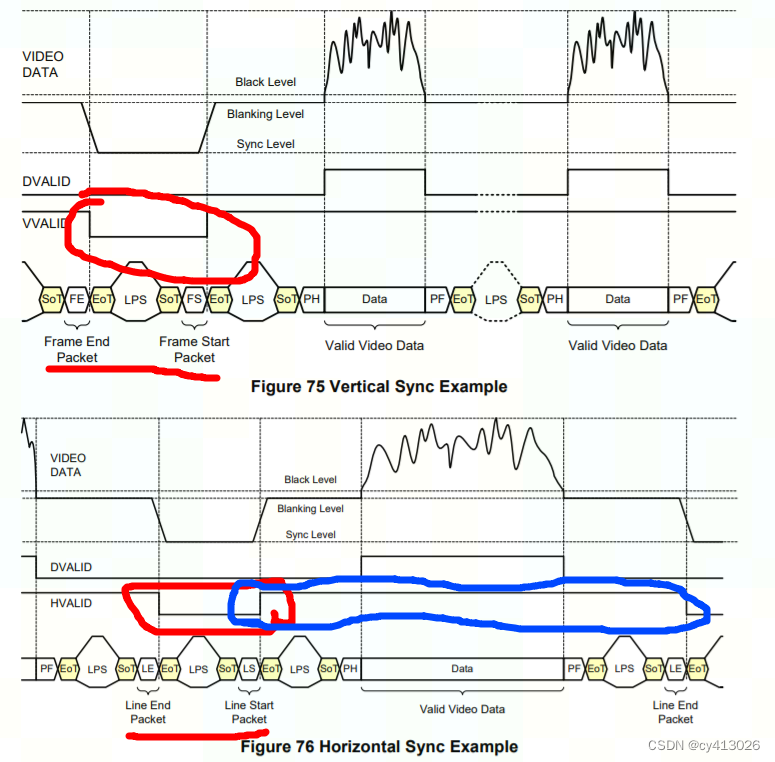

1.3.1.3 FS/FE LS/LE与V/Hsync

在需要精确的像素级别的V/HSync和blanking情况下,FS/FE, LS/LE短包的发送时间要满足对应图像格式/分辨率/帧率 的timing需求。如果不需要精确的timing信息FS/LS尽量靠近后面第一个数据长包,FE/LE尽量靠近前面最后一个数据长包。

如下图75 FE和下一个FS之间的间隔为帧间blanking,此时Vsync有效。图76的LE和下一个LS之间是水平blanking区间,此时Hsync有效,LS和对应LE之间为 line total,之间的长包payload为dataValid。

上面两图画的只有一个VC,且一行是一个长包。实际上因为csi传输是burst传输,CPHY的bitRate可以远大于clkpix,所以可以多VC传输的同时,满足对交织的多帧数据的timing需求。

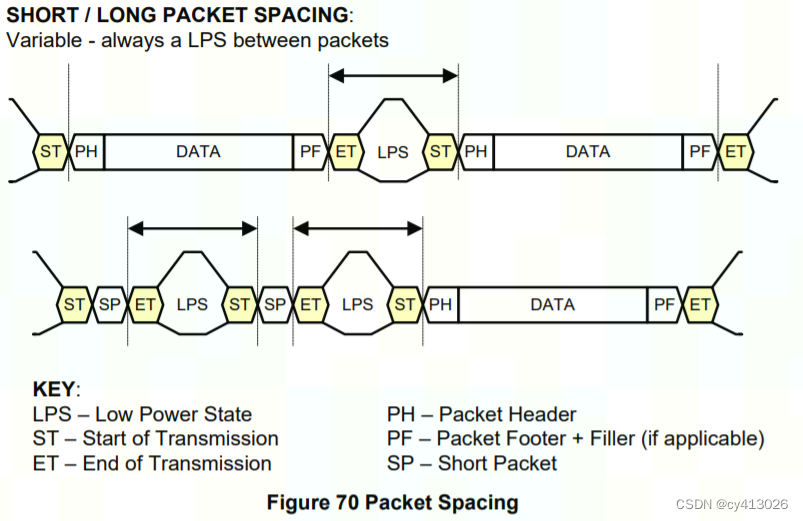

1.4 packet spacing包间距

所有的CSI2都应该支持在packet之间进入低功耗的操作。但是packet进入LP的操作有几个缺点:

- 切换速度慢,会影响传输效率

- HS和LP两套电压和电路,控制复杂

CSI2 V2.0之前都只支持packet之间进入LP。但是dsi一直支持连续包发送。这应该也和CSI2/DSI的特性有关

CSI2 只有Burst传输,图像一行就是一个LgP,所以有更多的时间进入LP

DSI一行可以分为多个LgP,所以允许连续发包比较合理。

所以在新的协议加入了一些新的特性。比如CSI2-v3.0 DPHY V2.5/CPHY V2.0【在此之前都只有LP mode】加入了LRTE/ALP

LRTE:Latency Reduction and Transport Efficiency 延迟减少和传输效率

ALP:Alternative Low power 备用低功耗

1.4.1 LRTE

LRTE包含两个部分:

- 减少数据包延迟(ILR: Interpacket Latency Reduction)

- 提高传输效率(Enhanced Transport Efficiency)

1.4.1.1 ILR

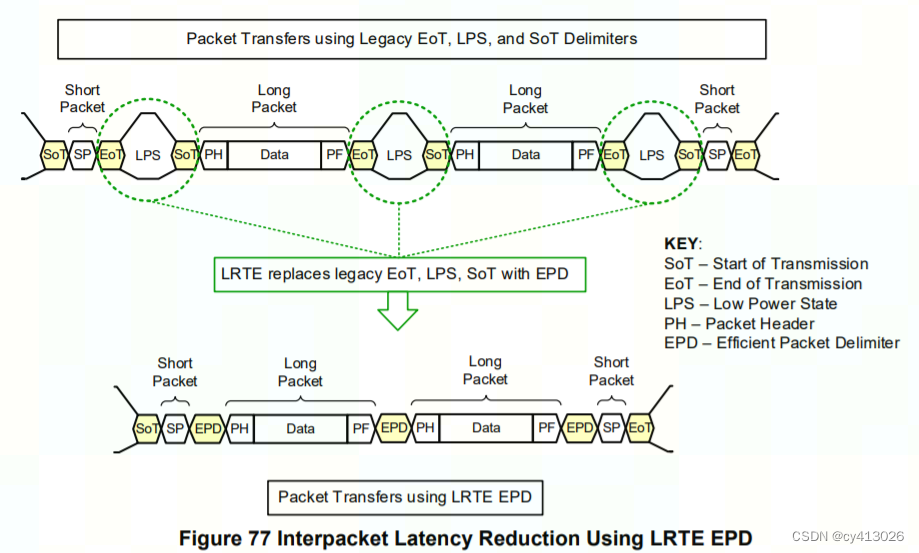

传统的长短包定界符是EOT,LPS和SOT,需要进行HS-LPS-HS的转换。一些先进的Camera通过减少这些定界符的开销而有效提高速度。

用更高效的包定界符(Efficient Packet Delimiter) EPD取代EOT LPS和SOT,可以避免HS-LPS-HS的转换。

EPD包含由协议层和PHY层两部分操作组成:

- PHY生成的Packet Delimiter Quick PDQ-------EPD必须组成部分

- protocol生成的Spacers,在PDQ之前-------这是EPD可选的

上图可以看出EOT-LPS-SOT被替换成了EPD,第一笔的Sot之后和最后一个Eot之前是没有EPD的。虽然协议不允许在最后一个Eot之前插入EPD,但是在满足一定条件下,可以在最后一个EOT之前插入protocol生成的Spacers。

对于CPHY的PDQ来说,PDQ复用syncWord

1.4.2 ALP

ALP已在下面文章中做了比较详细的介绍,这里不在展开。

CSI及CPHY的学习知识点_cy413026的博客-CSDN博客

1.5 LVLP(low Voltage low power)

1.6 USL:Unified Serial link 统一串行链路

1.7 Embedded packet 与SROI

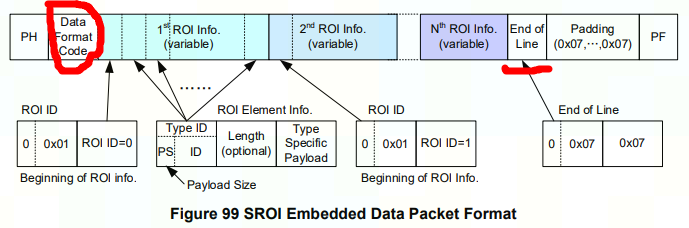

SROI(smart ROI)智能感兴趣区域,SROI信息的传输需要用到ROI的短包和embedded的数据长包。

embedded packet也是长包的一种,可以传输多种信息,DT可以是0x10~0x17的通用长包,也可以是0x30~0x37的自定义长包。为了和区分embedded packet到底传输的是什么,在embedded packet payload的第一字节传输一个Data Format Code,其中SROI的Data Format Code为0x0D,传输的是ROI 信息。

1.8 Frame Format Examples(图像帧格式)

对于csi来说,sensor采样数据无论是逐行扫描还是隔行扫描,soc的Video in模块只需要知道FS/FE和图像行的宽度就可以按图像帧处理数据.所以FS/FE是必须的而LS/LE不是必须的。video In模块基本不需要V/Hsync时序,就可以直接对图像数据进行图像处理和写DDR。

相比之下,显示才需要精确的syncTiming。而这个精确的syncTiming需要在source或者sink端重建,所以DSI有Burst发送和带sync信息/事件的non-burst传输两种情况。

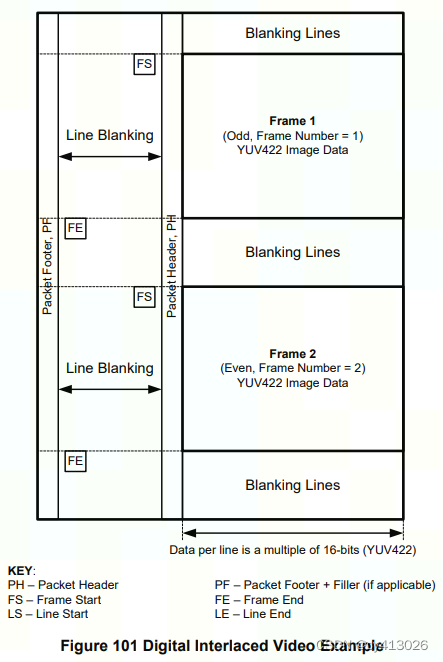

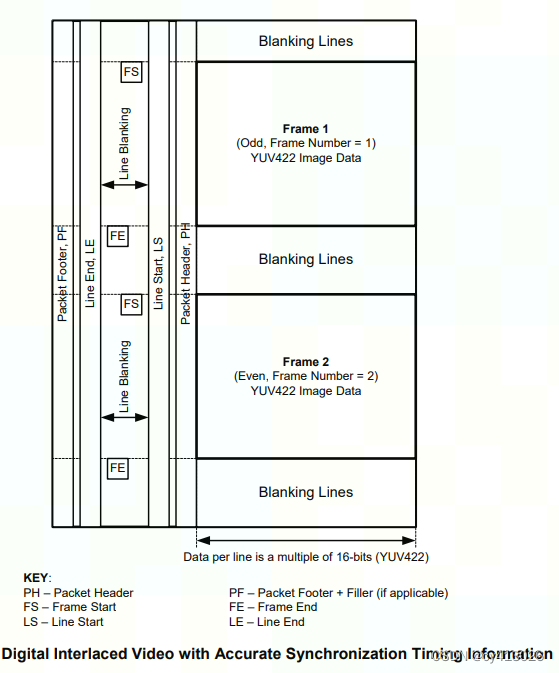

当然csi2也是可以支持像素级的syncTiming信息的。这时就需要LS/LE。这一节就简单介绍3种图像帧格式

从下面的介绍可以看出来interlaced 扫描的奇偶帧中间是blanking lines,1.8.2和1.8.3的图画出来是有PH和数据包的,所以认为这些blanking lines也是有数据包的,而Frame Blanking可以发送blanking packet也可以进入低功耗,也可以发送其他类型的packet。【需要注意的是line blanking不会发送任何数据包,只会进入低功耗】

1.8.1 通用图像帧格式

从下图可以看出embedded data

1.8.2 隔行扫描帧格式

1.8.3 隔行扫描帧+精确syncTiming

1.9 数据长包payload大小

短包的长度是固定的。对于长包分两种情况:

- 图像数据包,无论是YUV/RGB/RAW payload都只包含一行的长度,如果数据不是8bit对齐需要补齐

- 非图像数据包 包括自定义数据,USL,SROI 这些长包的数据长度可以是任意的.如果数据不是8bit对齐也需要补齐

另外对于图像数据包,在同一帧同一个VC的相同DT图像数据包里面的payload长度必须相同,YUV420是一个特例。

对于YUV的8/10 bit non-legacy格式,奇数行1,3,5只传输Y,偶数行2,4,6会传输UYVY。所以偶数行payload是奇数行的2倍。

对于legacy YUV420,奇数行传输UYY偶数行VYY,csi也是支持的,但是这种实现成本比较高,需要存储一行Y等到UV被采样出来一起发送。

1.10 Data interleaving

CSI2支持图像数据传输的两种交织情况:

- 相同VC,不同DT的packet的interleaving

- 不同VC之间的packet的interLeaving

1600

1600

暂无认证

暂无认证

2401_85689286: 对超算领域的重要意义不言而喻

努力成为一个硅农中: 请问如何才能让$sys识别sv中的字符串呢?

CSDN-Ada助手: 哇, 你的文章质量真不错,值得学习!不过这么高质量的文章, 还值得进一步提升, 以下的改进点你可以参考下: (1)增加除了各种控件外,文章正文的字数;(2)提升标题与正文的相关性。

fafa_Z: 您好 网盘文件能分享一下吗:共享存储体系和cache一致性。感谢!

yhc9785: 请教一下,假设调制频率是30K,频率偏移量为5000ppm,使用三角波是怎么确定这两个参数的呢